La nuova strategia di AMD per i data center e l’intelligenza artificiale

In occasione della Data Center and AI Technology Premiere, AMD ha annunciato l’aggiunta di due nuovi processori, ottimizzati per i carichi di lavoro, alla gamma di CPU EPYC di quarta generazione. Sfruttando la nuova architettura di core Zen 4c, le CPU per data center AMD EPYC 97X4 ottimizzate per il cloud estendono ulteriormente la serie di processori EPYC 9004. Inoltre, AMD ha annunciato i processori AMD EPYC di quarta generazione con tecnologia AMD 3D V-Cache, ideali per i carichi di lavoro tecnici più esigenti. “In un’era di calcolo ottimizzato per i carichi di lavoro, le nostre nuove CPU stanno spingendo i confini di ciò che è possibile fare nei data center, offrendo nuovi livelli di prestazioni, efficienza e scalabilità” ha dichiarato Forrest Norrod, vicepresidente esecutivo e direttore generale del Data Center Solutions Business Group di AMD.

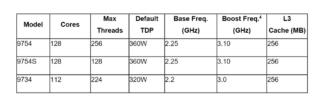

I carichi di lavoro nativi del cloud sono una classe di applicazioni in rapida crescita progettate con un’architettura cloud e vengono sviluppati, distribuiti e aggiornati rapidamente. I processori AMD EPYC 97X4 con un massimo di 128 core offrono prestazioni di throughput fino a 3,7 volte superiori per i principali carichi di lavoro cloud native rispetto ad Ampere. Inoltre, i processori AMD EPYC di quarta generazione con core Zen 4c offrono ai clienti un’efficienza energetica fino a 2,7 volte superiore e supportano un numero di container per server fino a 3 volte superiore per realizzare applicazioni cloud native su larga scala.

I processori AMD EPYC di quarta generazione con tecnologia AMD 3D V-Cache ampliano ulteriormente la serie di processori AMD EPYC 9004 per offrire la migliore CPU x86 al mondo per i carichi di lavoro di calcolo tecnico, come la fluidodinamica computazionale (CFD), l’analisi agli elementi finiti (FEA), l’automazione della progettazione elettronica (EDA) e l’analisi strutturale. Con un massimo di 96 core Zen 4 e una cache L3 da oltre 1 GB, i processori AMD di quarta generazione con AMD 3D V-Cache possono accelerare in modo significativo lo sviluppo dei prodotti, fornendo fino al doppio dei lavori di progettazione al giorno in Ansys CFX.

Sul palco della Data Center and AI Technology Premiere, Microsoft ha inoltre annunciato la disponibilità generale delle istanze Azure HBv4 e HX alimentate da processori AMD EPYC di quarta generazione con AMD 3D V-Cache. Ottimizzate per le applicazioni HPC più esigenti, le nuove istanze offrono un aumento delle prestazioni fino a 5 volte rispetto alla precedente generazione di istanze HBv3 e scalano fino a centinaia di migliaia di core CPU. L’intera gamma di processori AMD EPYC di quarta generazione è disponibile da oggi ed è compatibile per caratteristiche e socket con i sistemi basati sulle CPU della serie AMD EPYC 9004.

C’è poi stato spazio per una serie di annunci che illustrano la strategia AI Platform dell’azienda, che offre ai clienti un portafoglio di prodotti hardware dal cloud, all’edge e all’endpoint, con una profonda collaborazione software con il settore per sviluppare soluzioni IA scalabili e pervasive.

Gli annunci hanno riguardato la famiglia di acceleratori AMD Instinct MI300 Series tra cui l’acceleratore AMD Instinct MI300X, il più avanzato al mondo per l’IA generativa. Si basa sull’architettura di nuova generazione AMD CDNA 3 e supporta fino a 192 GB di memoria HBM3 per fornire l’efficienza di calcolo e di memoria necessaria per l’addestramento e l’inferenza di modelli linguistici di grandi dimensioni e per i carichi di lavoro dell’intelligenza artificiale generativa. Grazie all’ampia memoria di AMD Instinct MI300X, i clienti possono possono ora adattare modelli linguistici di grandi dimensioni come Falcon-40 su un singolo acceleratore MI300X5.

AMD ha presentato inoltre l’ecosistema software ROCm per gli acceleratori di data center, evidenziando la disponibilità e le collaborazioni con i leader del settore per creare un ecosistema software IA aperto. PyTorch ha parlato del lavoro svolto da AMD e dalla PyTorch Foundation per rendere completamente upstream lo stack software ROCm, fornendo un supporto immediato “day zero” con la release 5.4.2 di ROCm su tutti gli acceleratori AMD Instinct.

Questa integrazione consente agli sviluppatori di disporre di un’ampia gamma di modelli di intelligenza artificiale basati su PyTorch che sono compatibili e pronti all’uso “out of the box” sugli acceleratori AMD. Hugging Face, la principale piattaforma aperta per i costruttori di IA, ha infine annunciato che ottimizzerà migliaia di modelli Hugging Face sulle piattaforme AMD, dagli acceleratori AMD Instinct a processori AMD Ryzen e AMD EPYC, GPU AMD Radeon e processori adattivi Alveo.